### **VU Research Portal**

### **Programming Many-Cores on Multiple Levels of Abstraction**

Hijma, H.P.

2015

document version Publisher's PDF, also known as Version of record

Link to publication in VU Research Portal

*citation for published version (APA)* Hijma, H. P. (2015). *Programming Many-Cores on Multiple Levels of Abstraction*. [PhD-Thesis - Research and graduation internal, Vrije Universiteit Amsterdam].

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

E-mail address: vuresearchportal.ub@vu.nl

# Programming Many–Cores on Multiple Levels of Abstraction

Pieter Hijma

### **Programming Many-Cores**

on

### Multiple Levels of Abstraction

Pieter Hijma

### VRIJE UNIVERSITEIT

## Programming Many-Cores on Multiple Levels of Abstraction

### ACADEMISCH PROEFSCHRIFT

ter verkrijging van de graad Doctor aan de Vrije Universiteit Amsterdam, op gezag van de rector magnificus prof.dr. F.A. van der Duyn Schouten, in het openbaar te verdedigen ten overstaan van de promotiecommissie van de Faculteit der Exacte Wetenschappen op dinsdag 9 juni 2015 om 11.45 uur in de aula van de universiteit, De Boelelaan 1105

door

### Hein Pieter Hijma

geboren te Dokkum

| promotor:   | prof.dr.ir. H.E. Bal    |

|-------------|-------------------------|

| copromotor: | dr. R.V. van Nieuwpoort |

|             |                         |

members of the thesis committee:

dr. Rosa M. Badia prof.dr.ir Henk J. Sips prof.dr. Paul Klint dr. Clemens Grelck dr.-Ing.habil. Thilo Kielmann

This work was carried out in the ASCI graduate school. ASCI dissertation series number 329.

This thesis was realized with support from the Wijbenga-leen.

Cover image by Pieter Hijma, adapted from the photograph "wafer 3" from Santi: https://www.flickr.com/photos/s4nt1/15137081219. The photograph was licensed with the Creative Commons Attribution-ShareAlike 2.0 license: https://creativecommons.org/licenses/by-sa/2.0. The cover image is licensed with the same license, but version 4.0: http://creativecommons. org/licenses/by-sa/4.0.

Copyright  $\bigodot$  2015 by Pieter Hijma

### Acknowledgements

Although it has not been easy at times, I have learned so much these last years. I am very grateful for the faith and continuous support from my promotor Henri Bal and co-promotor Rob van Nieuwpoort. Henri and Rob, you have given me much freedom and from the beginning we have tried to balance this freedom with minimizing the risk by avoiding to implement a large compiler. We have failed in doing so, but I am now glad that we took those risks and I am happy with the end-result: this thesis.

I have been very lucky to receive much help from many people. Firstly, Ceriel Jacobs helped in virtually all my papers. In all cases I would start to implement my ideas, would realize after a while that it would take too much time for one person, after which Ceriel would step in and learn my completely undocumented code. This must not have been easy, especially with the Many-Core Levels (MCL) system as it had a very large code-base. However, Ceriel, for me it was invaluable to be able to discuss the low-level details with you.

Secondly, I want to thank the Software Analysis and Transformation (SWAT) team at the CWI. They invited me to come work at the CWI with their system Rascal in which I implemented MCL. Their direct and active support allowed me to learn Rascal fast. Rascal has been invaluable for prototyping my language designs and it helped me to work very quickly, allowing me to almost keep up with "a compiler pass a day". I want to thank Paul Klint, for his enthusiasm about me using Rascal; Jurgen Vinju, for working incredibly hard to fix bugs in Rascal; Tijs van der Storm, from whom I learned many things about programming languages; and Atze van der Ploeg. Atze, thanks for the countless discussions we have enjoyed. I learned much about my own ideas by trying to convince you that you were wrong, especially in reaction to your standard phrase: "Oh, that's trivial!". Let us not comment on how many times you actually were wrong, as it would start another discussion.

Furthermore, I want to thank my committee for finding time to take part in

my defense and to consider whether I deserve the degree of Ph.D.: Rosa Badia, Henk Sips, Paul Klint, Clemens Grelck, and Thilo Kielmann. Thank you for your kind words and your constructive feedback that allowed me to improve the thesis further.

I want to thank all my colleagues at the VU: My paranymphs Ben van Werkhoven and Stefan Vijzelaar: Ben, I am glad that after sharing the same office for so long (and after you left), we have finally started working together with a nice paper as outcome. Stefan, thank you for the nice collaboration in the Concurrency and Multithreading class. I hope the students learned many things, but in any case we learned more and more about concurrency each iteration. I want to thank all my office mates during the years for the enjoyable time: Albana Gaba, Suhail Yousaf, Christian Rossow, Rena Bakhshi, Ben, and Alessio Sclocco.

I want to thank Andy Tanenbaum for appreciating the proposal I wrote for the Research Proposal Writing class and notifying Henri Bal about it. This led to my Master project which transitioned into my Ph.D.; Kees van Reeuwijk for supervising me initially in the sync generator project; Kees Verstoep for keeping the DAS-4 always up, especially in paper deadline periods; and Wan Fokkink for working together on the Concurrency and Multithreading class and giving me the opportunity to do a guest lecture.

Alessandro Margara, I much enjoyed our discussions during the many bike rides to the swimming pool, even though I knew you would beat me in swimming afterwards. Thanks also for your feedback on the MCL papers from which I learned much; Roelof Kemp, thank you for the coffee moments. I especially remember the coffee breaks in the summer of 2012 in which you looked back on your Ph.D. time. This has influenced the way I worked; Timo van Kessel, I regret that we did not manage to work together on a paper but I wish you all the best; Remco Vermeulen, I admire the fact that you took even more risk than I did with the incredibly difficult subject that you chose.

Many thanks to everybody of Henri's group: Ismail El-Helw, Jacopo Urbani, Kaveh Razavi, Alex Uta, Ana Oprescu, Stefania Costache, Rutger Hofman, Daniela Remenska, and old colleages Nick Palmer, Frank Seinstra, Jason Maassen, Niels Drost, and Maarten van Meersbergen. Many thanks as well to all others in the Computer Systems group. Thank you Caroline Waij, for arranging many things so swiftly, from barbecues to printer paper.

The Netherlands eScience Center needs special mention as they allowed Rob van Nieuwpoort to continue supervising me. Thanks to Cees de Laat and Ana Varbanescu from the UvA for allowing me to continue in academia; Raphael Poss and Merijn Verstraaten for their interest in my work and discussing new angles for MCL I did not think about. I want to thank Zeno Gerardts, Pelle Barens, Ewald Snel, and Arjan Mieremet from the NFI for their interest in MCL and Cashmere and providing an interesting forensics application.

I want to thank my parents for always supporting but never pushing me, even when I took drastic decisions such as starting with a Computer Science study. I am very grateful for all the chances you offered me. My brother Durk, thanks for not taking such drastic decisions as starting a Computer Science study. Let us agree on me doing the programming, while you remain doing what you do so well.

Dear Dorine, thank you for all the support and thank you for accepting the too many times that I had to work: weekends, evenings, and nights. It has been amazing for me that we could talk about my computer science topics and that you would not only listen, but also understand and ask questions. It is not for nothing that you came up with the title "Cashmere" for my system. I am very grateful I have you in my life.

Finally, all my friends that showed support: Sandra, Mandana, Haiko, Thomas, Renée, Atze, Herman, Melanie, Remco, Steven, Martijn, Despo, Abhi, Gerard, Femke, Martin, Hannah, Maarten, Koen, and Alessandro, thank you for your understanding in case I was stressed or busy, probably both. I hope we can catch-up the lost time of the last few years after the defense. xii

### Contents

Acknowledgements

| Co       | onter | nts xi                                   | ii |

|----------|-------|------------------------------------------|----|

| 1        | Intr  | roduction                                | 1  |

|          | 1.1   | Background                               | 4  |

|          | 1.2   | Scope                                    | 6  |

|          | 1.3   | Problem Statement and Research Questions | 6  |

|          | 1.4   | Outline of this thesis                   | 7  |

| <b>2</b> | Ger   | nerating Synchronization Statements 1    | .1 |

|          | 2.1   | Introduction                             | 12 |

|          | 2.2   | The Satin programming model              | 13 |

|          | 2.3   | Problem description 1                    | 16 |

|          | 2.4   | -                                        | 19 |

|          |       | -                                        | 19 |

|          |       | ÷                                        | 20 |

|          | 2.5   | * -                                      | 26 |

|          |       |                                          | 29 |

|          | 2.6   |                                          | 31 |

|          |       |                                          | 32 |

|          |       |                                          | 34 |

|          |       |                                          | 35 |

|          |       |                                          | 36 |

|          | 2.7   |                                          | 36 |

|          | 2.8   | 8 8                                      | 37 |

|          | 2.9   |                                          | 38 |

$\mathbf{i}\mathbf{x}$

| 3 | $\mathbf{Ste}_{\mathbf{I}}$ | pwise-refinement for performance             | 41         |

|---|-----------------------------|----------------------------------------------|------------|

|   | 3.1                         | Introduction                                 | 42         |

|   | 3.2                         | Related work                                 | 44         |

|   |                             | 3.2.1 Programming Many-cores                 | 44         |

|   |                             | 3.2.2 Other related Work                     | 47         |

|   | 3.3                         | Stepwise-refinement for Performance          | 48         |

|   |                             | 3.3.1 Philosophy                             | 49         |

|   |                             | 3.3.2 Methodology                            | 50         |

|   | 3.4                         | Design of MCL                                | 51         |

|   |                             | 3.4.1 Overview                               | 52         |

|   |                             | 3.4.2 Hardware Description Language HDL      | 54         |

|   |                             | 3.4.3 Programming Language MCPL              | 57         |

|   |                             | 3.4.4 Compiler                               | 59         |

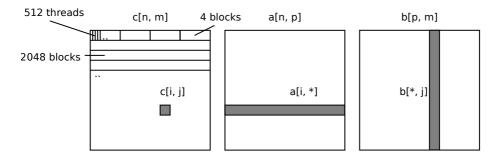

|   | 3.5                         | Example: Matrix Multiplication               | 61         |

|   |                             | 3.5.1 GTX480                                 | 65         |

|   |                             | 3.5.2 Xeon Phi                               | 72         |

|   |                             | 3.5.3 Summary                                | 75         |

|   | 3.6                         | Implementation                               | 76         |

|   |                             | 3.6.1 Translation between Abstraction Levels | 76         |

|   |                             | 3.6.2 Operation Statistics                   | 79         |

|   |                             | 3.6.3 Data Reuse Analysis                    | 80         |

|   |                             | 3.6.4 Cache Analysis                         | 82         |

|   |                             | 3.6.5 Performance Feedback Functions         | 83         |

|   | 3.7                         | Evaluation                                   | 84         |

|   | 3.8                         | Discussion                                   | 91         |

|   | 3.9                         | Conclusion                                   | 92         |

| 4 | Cas                         | hmere: Heterogeneous many-core computing     | 95         |

| 4 | 4.1                         | Introduction                                 | 95<br>96   |

|   | 4.1<br>4.2                  | Cashmere Programming Model                   | 90<br>98   |

|   | 4.2                         | 4.2.1 Satin                                  | 98<br>98   |

|   |                             | 4.2.1 Satin                                  | 98<br>100  |

|   |                             | 4.2.3 Cashmere programming model             | 100        |

|   | 4.3                         | Implementation                               | 100        |

|   | 4.0                         | 4.3.1 MCL                                    | 103        |

|   |                             | 4.3.1 MOL                                    | 103<br>104 |

|   | 4.4                         |                                              | 104<br>106 |

|   |                             |                                              |            |

|   | 4.5                         |                                              | 109        |

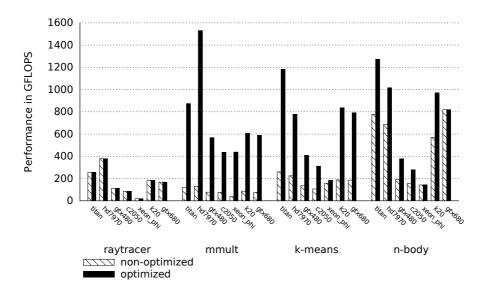

|   |                             | 4.5.1 Kernel performance                     | 109        |

\_\_\_\_\_

#### Contents

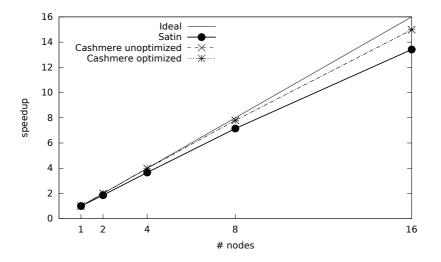

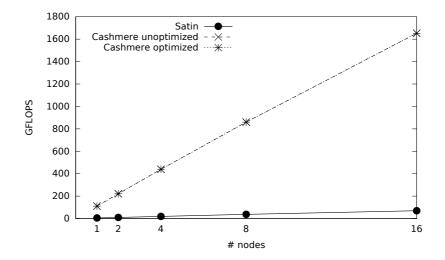

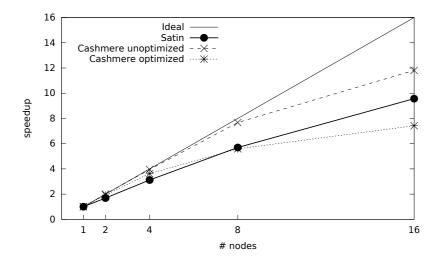

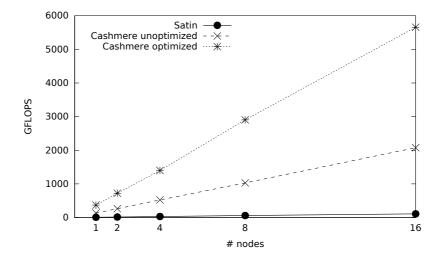

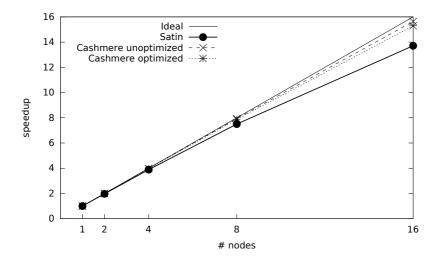

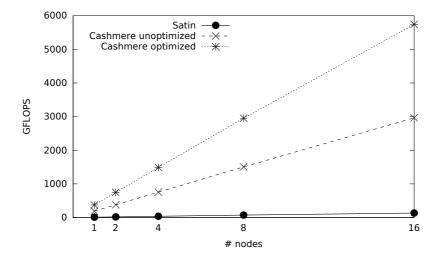

|            |       | 4.5.2 Scalability                        | 110 |

|------------|-------|------------------------------------------|-----|

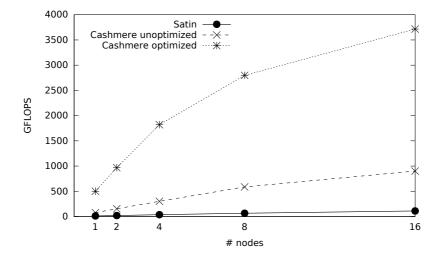

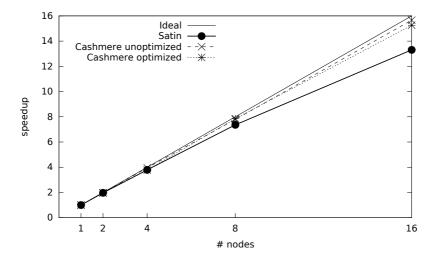

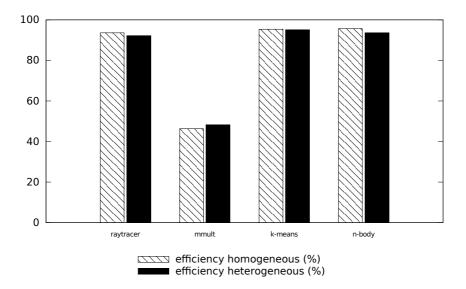

|            |       | 4.5.3 Heterogeneity                      | 111 |

|            | 4.6   | Related Work                             | 117 |

|            | 4.7   | Conclusion                               | 120 |

| <b>5</b>   | Con   | nclusions                                | 123 |

|            | 5.1   | Summary                                  | 123 |

|            | 5.2   | Future Directions                        | 126 |

|            |       | 5.2.1 Conclusions                        | 128 |

| A          | Mai   | ny-Core Levels Language Descriptions     | 129 |

|            | A.1   | Hardware Description Language HDL        | 129 |

|            | A.2   | Programming Language                     | 134 |

| в          | Tra   | nslating to a lower level of abstraction | 139 |

|            | B.1   | The top-level functions                  | 140 |

|            | B.2   | Finding equivalent ParGroups             | 141 |

|            | B.3   | Translating memory spaces                | 142 |

|            | B.4   | Translating ForEach statements           | 144 |

| References |       |                                          | 151 |

| Li         | st of | Publications                             | 163 |

| Sa         | men   | vatting                                  | 165 |

### Chapter 1

### Introduction

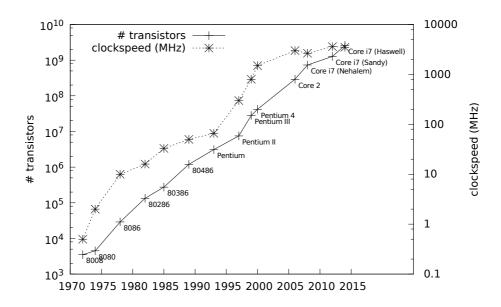

In the last decades we have witnessed an incredible increase in CPU performance. As a result, we were in the fortunate position of obtaining higher performance by running virtually the same software on newer generations of hardware. Fig. 1.1 illustrates Moore's Law, the exponential increase of the number of transistors over time that made this performance increase possible.

However, Fig. 1.1 also shows the clock-frequency over time. It shows that clock-frequency increased exponentially until the mid 2000s after which it leveled, while Moore's Law remained as before. Thus, every 18 months the number of transistors that we could fit on a die increased, but we were not able to increase the clock-speed due to power dissipation excesses. This meant a major change in the design of processors: the solution was to fit multiple processors or cores on one die running on a lower clock-frequency and therefore reducing the power dissipation. We call these processors *multi-core* processors (starting from "Core 2" in Fig. 1.1).

This was a fundamental change from a software viewpoint because from that moment processors exposed *parallelism* to the programmer. In fact, the traditional single-core machines were already highly parallel machines with much logic dedicated to optimize *sequential* instruction streams. However, to gain the same performance increase associated with the increase of the number of transistors for *multi-core* processors, the programmer has to offer the processor multiple parallel instruction streams. In other words, traditional sequential software will not run faster automatically on multi-core processors, but the software has to be made parallel to benefit from the increased performance of the multi-core processors.

Figure 1.1: Development of processors over time (source Intel).

So far, we have seen two types of processors: traditional *single-core* processors, with much logic dedicated to optimize sequential programs and *multi-core* processors with multiple cores of which each core has still much logic dedicated to optimize sequential programs. It exposes parallelism to the programmer, but in a moderate way (the number of cores). This thesis, however, studies how to program *many-core* processors. Instead of dedicating logic to optimize sequential programs as single-core and multi-core processors do, many-core processors use most logic to expose a high degree of parallelism to the programmer in the form of many simple cores. Its programs need to be highly parallel, but in return the programmer is able to achieve much higher performance than with multi-core processors because a large degree of the logic of a chip is used for computing instead of analyzing sequential instruction streams.

Examples of the many-core processors that we use in this thesis are the Graphics Processing Unit (GPU) and the Xeon Phi from Intel. GPUs have become more general over the years and are now often used to accelerate large scientific codes or other compute intensive applications. The Xeon Phi is also typically used in this way. Both processors have in common that they expose

large amounts and multiple levels of parallelism. Typically, they provide tens of cores that need hundreds of parallel tasks to keep the device busy. Each core then exposes another level of parallelism in the form of small, simple dataparallel cores or vector processor units.

The design of these processors is important for the energy consumption. Because most of the logic of the chip is dedicated to computation and not optimizing instruction streams, many-cores deliver much higher performance per Watt [1, 2]. This is not only important for mobile devices, but also for supercomputers that start to use unacceptable amounts of energy. From 1972 to 2007, the performance of supercomputers increased 10,000 fold, but the performance per Watt ratio only increased 300 fold. Nowadays, supercomputers draw power equivalent to small cities [3]. It is clear that many-cores provide an opportunity in this context and many supercomputers are already fitted with many-core processors today. It is highly likely that massively parallel hardware in the form of many-cores will play an important role in computing in the future.

However, many-core processors are difficult to program for multiple reasons. The only goal of many-core processors is obtaining high performance. They expose a complicated interface to the programmer with many levels of parallelism and a complicated memory hierarchy, all meant to reach high performance. They do not have a standardized instruction set as single-core and multi-core processors have, there are many different kinds of many-core processors, and the hardware evolves quickly. Because of the many levels of parallelism that closely interact with the memory subsystem, the performance of a program can improve drastically if it accounts for the limitations of the processor and makes proper use of the available hardware. Therefore, optimizing a program for many-cores is often beneficial but also very difficult.

This thesis proposes solutions for this programming problem. It takes a fundamental approach: It considers the hardware limitations that we face, for example the memory wall (computation speed increases faster than memory access speed) and the energy wall (clock-frequency cannot increase any further) as programming problems. Thus, we consider the *single-core era* to be a fortunate situation in which the increase of clock-frequency meant automatic performance gains without changing the software, but it was never truly sustainable; *multi-core hardware* shows a transition from offering a sequential hardware interface to a parallel hardware interface with still much logic to optimize sequential programs. This transition will ultimately lead to hardware that will not make any compromises in its interface to programmers to overcome the hardware limitations that we face. This thesis considers *many-core processors* as a first manifestation of this kind of hardware. To summarize what this thesis is about: Eventually we will reach the limits of hardware which will result in a complicated interface to the programmer, making this hardware increasingly more difficult to program. The main question that this thesis tries to answer is how to effectively program this hardware while still achieving high performance.

The next section describes some background to clarify why we believe that the shift from single-core and multi-core processors to many-core processors should change the traditional view on the role of programmers and compilers. In Sec. 1.2 we explain the scope of the thesis and Sec. 1.3 defines the problem and presents the research questions. Section 1.4 presents the outline of the thesis.

#### 1.1 Background

Computer hardware exposes a set of instructions that one can execute on this hardware. Programming means to find a sequence of instructions such that a problem is solved. Problems can be solved in many ways and the particular way a problem is solved is called an algorithm. Given an algorithm for solving a problem, programming is finding the sequence of instructions that implements this algorithm.

Usually, the exposed instructions are very low level and cumbersome to use. As a result, a fundamental step in computer science is to find a sequence of instructions that occurs often and find a simple expression that can be translated into this sequences of instructions. For example, adding two numbers in memory locations  $\mathbf{a}$  and  $\mathbf{b}$  and loading the result in memory location  $\mathbf{c}$  could be encoded into the following instructions:

mov(r1, a)

mov(r2, b)

add(r1, r2)

mov(c, r1)

The first two instructions move the value in memory locations  $\mathbf{a}$  and  $\mathbf{b}$  into registers  $\mathbf{r1}$  and  $\mathbf{r2}$  as an add instruction cannot operate directly on memory but only on special purpose registers. The add instructions computes the addition and puts the result in register  $\mathbf{r1}$  that we move back into memory location  $\mathbf{c}$  in the final instruction. Because this is cumbersome we prefer an expression such as

c = a + b

which computes the same. We call this a higher-level abstraction because it abstracts away the movement from and to registers. The task of translating

#### 1.1 Background

a higher-level abstraction to the lower-level representation is performed by a compiler. In a way, the compiler exposes a new interface to the hardware that matches better with how we think.

Another task of the compiler is optimizing code. For example, it may be natural for us to write an expression as

c = (a + b) \* (a + b)

The compiler may be able to perform common sub-expression elimination and transforming this code into

t = a + b c = t \* t

removing one addition. This seems like a good idea, but it is important to note that by doing this, the compiler makes certain assumptions about the hardware. In this case, the compiler assumes that using a temporary memory location t is beneficial for the overall performance. However, dependent on the hardware, this may not be the case. For example in many-core hardware, it may be faster to recompute the value than reusing a register.

This scheme, consisting of

- provide the programmer high-level abstractions,

- automatically translate to lower-level representations and optimize the instructions where possible, and

- run the instructions while extracting parallelism from the instructionstream on the fly in hardware

has been very successful in the single-core era because 1) the interface of hardware has not changed much over the years, and 2) obtaining higher performance could be achieved by buying newer hardware.

Due to the increasing complexity of the hardware interface that is exposed to programmers, we reconsider the responsibilities in achieving high performance in this thesis. We envision that programmers will be responsible for achieving performance and expressing parallelism. We change the role of compilers as being a black box translator and optimizer to a more advisory role where programmers have much control. Because performance becomes a software problem and not a hardware problem we also reconsider high-level abstractions in relation to control over the hardware.

#### 1.2 Scope

In this thesis we study the problem of programming many-cores. Programming in itself is already very challenging. Humans are experts in communicating through natural language where a context is always implied to resolve the many ambiguities that natural language contains. However, to communicate with (read: programming) a machine we need formal languages that leave no room for ambiguities. For humans, it is very challenging to adapt to these formal languages and remove all ambiguities, especially when programs become larger and more complex [4].

It is also important to note that software is not only written for machines, but also for humans. Typically, software grows slowly and remains in use much longer than anticipated. This means that software has to be maintained. Already in 1968 it was clear that the cost of software engineers writing and maintaining codes exceeded the cost of hardware [5].

Sequential programming is challenging, but parallel programming is even more demanding. Instead of expressing the steps for one sequential program, programmers have to decide on the granularity of parallelism, how the parallel tasks interact and how shared data can be protected. Lee explains the many problems that can arise in parallel programming [6].

Within the parallel programming field, this thesis focuses on programming many-cores. As explained above, many-cores expose all kinds of architectural intricacies to achieve high performance and the performance differences can be quite large when a program is well-balanced in how the hardware is used.

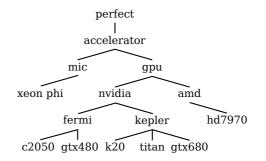

In general, many-core processors will be used as components in larger systems such as supercomputers or clusters, so we also study how to program *clusters* of many-cores. More specifically, as many-core hardware shows much variety and evolves fast, we study clusters of *heterogeneous* many-core processors. We expect that in the near future heterogeneity of many-cores in clusters can play an important roll in improving power consumption and performance.

### **1.3** Problem Statement and Research Questions

The limitations in hardware (memory wall, energy wall) will have an effect on the design of hardware that will eventually have repercussions on how to program these chips. Many-core hardware is the first manifestation of hardware that provides little compromise in the hardware design and the interface that is exposed to programmers. The main research question of this thesis is: • How can we support programmers in their responsibility to achieve high performance from many-core hardware?

There are several sub-questions that follow from this question that we try to answer in the following chapters:

- 1. What are important design considerations for parallel programming models and their compiler analyses?

- 2. How to balance control over hardware with raising the level of abstraction?

- 3. How can we manage the many different types of many-core hardware that exist?

- 4. Can we provide programmers a structured approach with which a programming system can assist them to achieve high performance?

- 5. How to achieve good scalability when programming *clusters* of manycores?

- 6. How to program *heterogeneous* many-core clusters?

### **1.4** Outline of this thesis

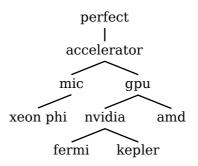

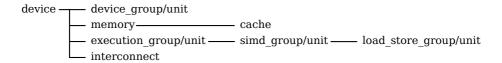

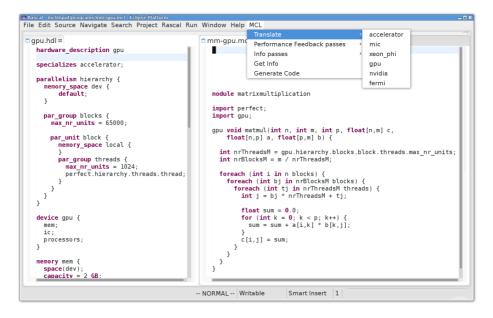

The major contribution of this thesis is a methodology for programming manycore devices that we call "Stepwise-refinement for performance". We present two programming systems for many-core devices: Many-Core Levels (MCL) and Cashmere. MCL focuses on writing computational kernels for many-core devices on multiple levels of abstractions and as a system, it supports the *stepwiserefinement for performance* methodology. We define a computational kernel, or just kernel, as a compute-intensive set of functions within an application that as a whole can be run on a many-core device. Cashmere combines MCL with Satin, an existing divide-and-conquer programming model [7] to bring the many-core compute power to clusters of heterogeneous many-core devices.

**Chapter 2** This chapter does not yet focus on many-core devices but presents an analysis of Satin programs. This chapter gives an answer to research question 1 and has important conclusions that influenced the design of MCL and Cashmere. Most importantly, it led to the insight that it may be preferable to have compilers in a more advisory role while programmers remain in control. This is a major theme throughout the thesis. This chapter is based on the following publications:

Automatically Inserting Synchronization Statements in Divide-and-Conquer Programs. Pieter Hijma, Rob V. van Nieuwpoort, Ceriel J.H. Jacobs, and Henri E. Bal. In 2011 IEEE International Symposium on Parallel and Distributed Processing Workshops and Phd Forum (IPDPSW), pages 1233–1241, May 2011.

Generating synchronization statements in divide-and-conquer programs. Pieter Hijma, Rob V. van Nieuwpoort, Ceriel J.H. Jacobs, and Henri E. Bal. *Parallel Computing*, 38(1-2):75 – 89, January–February 2012.

**Chapter 3** This chapter answers research question 2, 3, and 4. It presents the Many-Core Levels programming system that supports the *stepwise-refinement* for performance methodology with which programmers can optimize computational kernels guided by the compiler. The novelty in MCL is that it supports multiple levels of abstraction, giving programmers a trade-off in portability and program maintainability against control to reach high performance. This chapter is adapted from the following publications:

Programming Many-Cores on Multiple Levels of Abstraction. Pieter Hijma, Rob V. van Nieuwpoort, and Henri E. Bal. In *Proceedings of* the 5th USENIX Conference on Hot Topics in Parallelism (Poster presentation), HotPar '13, pages 1–7, Berkeley, CA, USA, 2013. USENIX Association.

Stepwise-refinement for performance: a methodology for many-core programming. Pieter Hijma, Rob V. van Nieuwpoort, Ceriel J.H. Jacobs, and Henri E. Bal. *Concurrency and Computation: Practice and Experience*, 2015. http://dx.doi.org/10.1002/cpe.3416.

**Chapter 4** In this chapter we introduce Cashmere, a programming system that combines MCL with Satin's divide-and-conquer programming model to program heterogeneous clusters of many-core devices. The major contribution of this chapter is a programming system that achieves good scalability even with many-cores that vary widely in architectures and performance. This chapters answers research questions 5 and 6 and is based on the following publication:

Cashmere: Heterogeneous Many-Core Computing. Pieter Hijma, Ceriel J.H. Jacobs, Rob V. van Nieuwpoort, and Henri E. Bal. In 29th IEEE International Parallel & Distributed Processing Symposium (IPDPS 2015), 25-29 May 2015, Hyderabad, India., 2015.

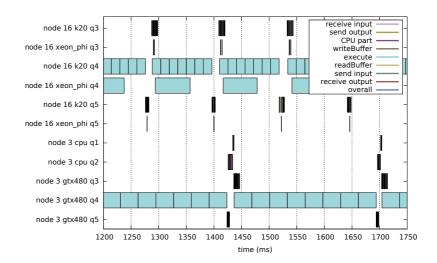

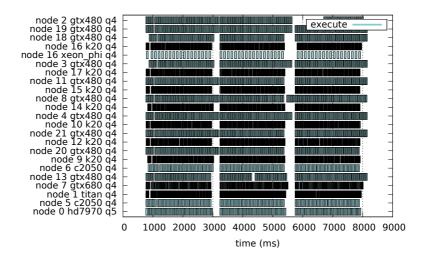

**Chapter 5** This last chapter presents a summary of the thesis, our conclusions, and future directions. We conclude that MCL and Cashmere provide promising solutions to support programmers in their responsibility to extract performance from many-core devices, whether or not arranged in cluster computers. MCL provides a trade-off in control over hardware and the level of abstraction, and it supports a methodology that gives programmers insight in the compiler and the performance of their application in relation to the hardware. Cashmere provides a solution for heterogeneous many-core clusters with automatic load-balancing and detailed performance feedback in the form of Gantt-charts of the execution.

### Chapter 2

## Generating synchronization statements in divide-and-conquer programs

Divide-and-conquer is a well-known and important programming model that supports efficient execution of parallel applications on multi-cores, clusters, and grids. In divide-and-conquer systems such as Satin or Cilk, recursive calls are automatically transformed into jobs that execute asynchronously. Since the calls are non-blocking, consecutive calls are the source of parallelism. However, programmers have to manually enforce synchronization with sync statements that indicate where the system has to wait for the result of the asynchronous jobs.

In this chapter, we investigate the feasibility of automatically inserting sync statements to relieve programmers of the burden of thinking about synchronization. We investigate whether correctness can be guaranteed and to what extent the amount of parallelism is reduced when synchronization statements are inserted automatically. We discuss the code analysis algorithms that are needed in detail.

To evaluate our approach, we have extended the Satin divide-and-conquer system, which targets efficient execution on grids, with a sync generator. Our experiments show that, with our analysis, we can automatically generate synchronization statements in virtually all real-life cases: in 31 out of 35 realworld applications the **sync** statements are placed optimally. The automatic placement is correct in all cases, and in one case the sync generator corrected synchronization errors in an application (FFT).

Finally, this chapter presents important design considerations that influenced the design of MCL and Cashmere: most importantly, we conclude that programmers have application knowledge that compilers lack and that compilers can overlook optimizations because they have to be conservative to guarantee correctness.

### 2.1 Introduction

Writing parallel programs is difficult in general. Writing parallel programs that execute efficiently on multiple clusters or clouds is even more demanding. Satin [7] makes cross-grid computing accessible to programmers who are not parallel programming experts. It allows programmers to write parallel programs without much effort by offering a sequential divide-and-conquer programming model. Typical applications for Satin are large scientific computations or other compute-intensive problems.

In Satin, programmers annotate recursive methods to indicate that calls to these methods are spawnable, which means that they can be executed asynchronously. Consecutive spawnable method calls create parallelism in the program. These method calls are transformed into jobs that are executed efficiently on grids or clouds using the Ibis platform [8].

However, since spawnable method calls are non-blocking, programmers also have to annotate where in the program the system has to block until the results of the jobs are available. Programmers indicate this by carefully inserting sync() statements. Placing sync statements too soon results in less parallelism than possible and placing them too late gives incorrect results. Our goal is to make grid computing even more accessible to programmers who are not parallel programming experts by making sync insertion automatic.

Having automatic sync insertion, by means of a sync generator, means that programmers no longer have to think about synchronization. The following questions arise: can syncs always be automatically inserted in such a way that the resulting program is correct; how much parallelism can be obtained; and what analysis is needed to accomplish this.

We found that the implementation of the sync generator program is able

to insert sync statements in such a way that the resulting program is always correct, but alias and control-flow analysis are needed to accomplish this. More extensive analysis will not lead to optimal placement in all cases: programmers sometimes *deliberately* use unsynchronized variables for performance reasons. An automatic generator cannot determine this.

In practice, our sync generator achieves excellent results. We tested the sync generator on 35 pre-existing real-world Satin applications. In 31 of them, the sync generator found the optimal locations for the sync statements. In all but one of the remaining cases, the sync generator gave a warning that the placement was likely suboptimal. In one case, it even corrected an originally incorrect application (FFT).

Our contributions are the following:

- We make implementing parallel divide-and-conquer applications even more effortless than before. Programmers only have to indicate parallel methods but not the synchronization points.

- We offer a good understanding of the problems involving automatically inserting synchronization statements.

- We provide a working implementation in the form of a compilation pass for the Satin compiler that generates synchronization statements automatically.

- We answer research question 1: What are important design considerations for parallel programming models and their compiler analyses?

The following section discusses the Satin programming model and explains some basic concepts. Section 2.3 defines the problem in detail and Sec. 2.4 discusses the implementation of the sync generator. We evaluate the sync generator in Sec. 2.5 using 35 real-world Satin applications while Sec. 2.6 discuss the results and presents important design considerations that affected the design of MCL and Cashmere. Section 2.8 describes related work after which the chapter concludes.

### 2.2 The Satin programming model

This section briefly introduces the Satin programming model. Satin [7] is a divide-and-conquer framework similar to Cilk [9]. The main differences are that

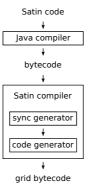

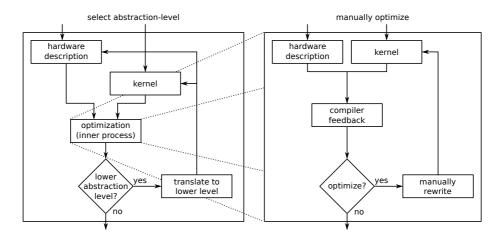

Figure 2.1: Compiler procedure with automatic sync generation.

programs are written in Java instead of Cilk, a C derivative, and that programs are deployed on a grid and not on shared memory systems.

The Satin compiler rewrites Satin programs in such a way that they can run in parallel on grids and clouds using Ibis [8]. Ibis is an environment that provides communication primitives to compute nodes in a grid. Rewriting Satin programs is performed with help of the bytecode rewriting library BCEL [10].

In order to create parallelism in a Satin program, programmers have to make some annotations. They have to indicate which methods are spawnable to ensure that the Satin compiler will rewrite those methods to versions that spawn jobs on the grid. The second annotation programmers have to make is a special sync() statement which is a barrier local to the method. The system will block at the sync statement until all results of the spawnable calls in the current method have become available. A node that blocks in a sync may execute jobs resulting from spawnable calls in the meantime.

The Java type and class systems provide all means to annotate Satin programs. Programmers create spawnable classes by extending the class ibis. satin.SatinObject that provides methods such as sync(). Programmers can also create an interface that extends ibis.satin.Spawnable. The method calls of the methods that are declared in this interface will be rewritten by the Satin compiler and executed in parallel.

The procedure from writing to deploying a Satin program is as follows: programmers write a sequential recursive program in Java and annotate the (possibly recursive) calls that have to be spawnable. They also place sync statements

```

1 interface SpawnProg extends ibis.satin.Spawnable {

\mathbf{2}

int spawningMethod(Data data);

3 }

4

5 int spawningMethod(Data data) {

6

if (stopCondition) return 0;

7

8

int result1 = spawningMethod(data.part1);

9

int result2 = spawningMethod(data.part2);

10

11

sync();

12

return result1 + result2;

13 }

```

Figure 2.2: A basic Satin program.

in places where the program has to wait for the results of the spawnable calls. The program is compiled to normal, sequential Java bytecode. This serves as input for the Satin compiler that rewrites the bytecode in such a way that Satin jobs are spawned. The application is now ready to be deployed on the grid.

The procedure in combination with the sync generator differs slightly and is depicted in Fig. 2.1. Again, programmers write a sequential recursive program but leave out the sync statements. They compile the program to ordinary bytecode. The Satin compiler takes the Java bytecode as input and generates sync statements in an extra compiler pass. It then rewrites the bytecode so that it spawns Satin jobs. It is still an option to insert sync statements manually. The sync generator will ignore methods that already contain sync statements.

Throughout the rest of the document the following terms will be used: A *spawning class* is a class that contains spawning methods. A *spawning method* is a method that contains *spawnable calls*. A *spawnable call* is an invocation of a method with a *spawnable method signature*. This is the signature of the method annotated by the programmer to be spawnable. A *sync statement* is a local barrier synchronization primitive which makes sure that all spawnable calls have returned their values.

Parameters of spawnable method signatures need to be serializable. Serializable classes provide a means to create a deep copy of the object including all objects that are referenced within the object and even cycles between these references. This allows applications to store objects on disk or transfer objects over the network. This last feature is used by the Satin runtime when a spawnable call is to be executed on a different node in the grid. Satin serializes every object in the argument list of the spawnable call to transfer the objects over the network.

Figure 2.2 depicts a typical Satin program. On line 2, spawningMethod() is marked to be a spawnable method, as it is defined in an interface that extends ibis.satin.Spawnable. The method on line 5 is a *spawning method*, because it contains two *spawnable calls* on line 8 and 9 (two recursive calls). These calls are non-blocking, and as a result the two calls run in parallel. At the statement in line 8, the Satin runtime may serialize the argument data.part1 depending on whether the data will be sent over the network or stays on the current node. It then creates a job, spawns the job, and returns to do the same for the spawnable call on line 9. The system will block at the sync() statement on line 11 until both parallel calls have finished and returned their results into result1 and result2. The method can now safely return the sum of result1 and result2.

Besides returning values using the **return** statement, a spawning method can also return using exceptions. Figure 2.3 illustrates this. The non-blocking spawning method is called on line 10 in the **try** block, and the program continues immediately beyond the **catch** clause. It executes the second **try** block, calling the second spawnable call on line 17 in parallel. The program continues beyond the **catch** clause and blocks on the **sync()**. When the first spawnable call has finished and the result has been thrown, a new thread stores the results in local variables in the catch block on line 12 and returns from the method. When this has happened for all spawnable calls, the main thread that blocked on the sync can continue and throw the result of this method.

This exception mechanism allows applications to perform work immediately after a spawning call has finished and is often used for speculative parallelism. An example is a parallel search. As soon as a spawnable call locates the item that is searched for and throws an exception, the new thread in the catch block can abort the other spawnable calls in order to prevent that more items are searched than necessary.

#### 2.3 Problem description

The sync generator's objective is to determine a suitable location for sync statements. Results of spawnable calls are generally stored temporarily to allow parallelism. For instance, on lines 8 and 9 in Fig. 2.2, the two spawnable calls store the results in result1 and result2. Sync statements should precede the part of the code where these results are used again. Therefore, because result1 and result2 are used again on line 12, there is a sync statement on line 11.

```

1 interface SpawnProg extends ibis.satin.Spawnable {

\mathbf{2}

void spawningMethod() throws Result;

3 }

4

5 void spawningMethod() throws Result {

6

if (stopCondition) throw new Result();

7

8

int result1, result2;

9

try {

10

spawningMethod();

11

}

12

catch (Result r) {

13

result1 = r.result;

14

return;

}

15

16

try {

17

spawningMethod();

18

}

19

catch (Result r) {

20

result2 = r.result;

21

return;

22

}

23

24

sync();

25

26

Result finalResult = new Result();

27

finalResult.result = result1 + result2;

28

throw finalResult;

29 }

```

Figure 2.3: A basic Satin program throwing exceptions.

Placing the sync statements too soon may reduce parallelism. For example, placing sync statements between lines 8 and 9 and after line 9 in Fig. 2.2 results in sequential execution of the two spawnable calls. Placing sync statements too late, after result1 and result2 have been used again, can lead to incorrect results.

The implementation of the sync generator focuses first of all on correctness. The main question is: is it possible to create a sync generator compilation pass that inserts sync statements in such a way that the resulting program is guaranteed to be correct? Correctness in this sense means that the placement of sync statements is such that the parallel version delivers the same results as the sequential version.

The second issue is then: is it possible to find a location for the sync statements in such a way that parallelism is created? If this is true, then the question is how optimal the placement is. Other questions are whether this can be achieved in a way that does not require complicated analysis or results in many spurious sync statements.

The sync generator operates under the assumption that it has as input all classes that are needed to determine which classes are spawning classes. In addition, there are some assumptions about spawnable calls. Figures 2.2, 2.3, and 2.4 show parts of typical Satin programs using return values, exceptions, and loops respectively.

A spawnable call can return in three ways. The spawnable method signature can be of type void. It then returns with an empty return statement. The second way is by returning a value using the return keyword. This happens in Fig. 2.2 and Fig. 2.4. Finally, it can return using exceptions as shown in Fig. 2.3.

In Satin, it is not possible to return values via parameters. Spawnable calls have either call-by-reference or call-by-value semantics, depending on whether a spawnable call is executed on the current node or on a different node in the grid respectively. In the latter case, the Satin runtime serializes the arguments of the spawnable call to send them over the network. It is undefined which mechanism is used, and therefore, programmers cannot assume call-by-reference or call-byvalue semantics.

For example in Fig. 2.2, programmers cannot rely on storing information in the data parameter at line 5 in order to make this information available to the method that called this method. The calling method may be on a different machine in the grid and in that case will not receive the information. So, to communicate information to the calling method, programmers need to either return values or throw exceptions.

Return values from spawnable calls are likely to be stored in local variables to allow parallelism, but this may not be the case. Also, these local variables may not be loaded again. In this case and the case that the spawnable call is of type void, the sync generator needs to place a sync as last instruction of the spawning method.

To conclude the boundaries for the sync generator, it is not an issue when multiple syncs are placed behind each other. The system will notice during the sync that there are no spawnable calls running and will just continue without any problem. It is also no problem to have sync statements when no spawnable call will be called. The overhead of these sync statements is negligible.

#### 2.4 Implementation

```

1 int spawningMethod() {

\mathbf{2}

if (stopCondition) return 0;

3

4

int[] results = new int[NR_SPAWNS];

5

int finalResult = 0;

6

7

for (int i = 0; i < results.length; i++) {</pre>

8

results[i] = spawningMethod();

}

9

10

11

sync();

12

for (int i = 0; i < results.length; i++) {</pre>

13

finalResult += results[i];

14

7

15

16

return finalResult;

17 }

```

Figure 2.4: A basic Satin program using loops.

### 2.4 Implementation

The sync generator analyzes Java bytecode with help of the BCEL bytecode rewriting library [10]. It implements each of the terms *spawning class*, *spawning method*, *spawnable call*, and *spawnable method signature* introduced in Sec. 2.2 as classes that hold all necessary information to do the analysis. The implementation also provides extensive debugging capabilities, a library to analyze control-flow graphs, and utilities to inspect the bytecode of classes and control-flow graphs. The implementation is written in Java and is about 4400 lines of code including comments and whitespace.

The first subsection describes the basic algorithm of the sync generator compilation pass. The second subsection discusses several analysis strategies and gives insight into which problems need to be solved to automatically generate sync statements.

#### 2.4.1 Basic algorithm

The basic algorithm of the sync generator is composed of three phases: the recording phase, the analysis phase, and the generator phase. During the recording phase, the sync generator reads in all class files. Next, it finds all spawnable method signatures from the interfaces and it then tries to create spawning classes

for every class file. This succeeds if the class contains spawning methods.

For a spawning method, the recording phase records all spawnable calls, and for every spawnable call, it keeps track of:

- the invoke instruction of the spawnable call

- the load instruction of the object reference on which the spawnable call is invoked

- the indices of the local variables in which the results are stored

A spawnable call tracks multiple local variables in case an exception is thrown. The catch block may store results in multiple local variables and subsequent loads of these local variables require a sync statement.

When the result is stored into an array or a field of an object, the analysis uses the local variable index of the object reference. This means that when a spawnable call stores into a field of **this**, the analysis tracks the local variable index of the **this** reference. In case the result is stored into a static variable, the analysis will default to no parallelism.

The analysis phase (discussed in detail in the following subsection) takes as input a spawning method and proposes one or more places to insert a sync statement. The generator phase will then insert a sync statement at those places.

### 2.4.2 Analysis phase

On the basis of four strategies that we employ in the analysis phase, we discuss the problems involved in automatically generating sync statements. The analysis phase takes as input a spawning method and the spawnable calls with the information provided by the recording phase. The analysis phase returns the instructions in front of which sync statements need to be inserted.

#### Fallback strategy

The fallback strategy is used when all other analysis fails. It proposes sync statements immediately behind the spawnable calls. This provides us guaranteed correctness as the resulting program is equivalent to the sequential program. However, this also means that there is no parallelism.

```

1 result1 = spawnableMethod();

2 result2 = spawnableMethod();

3

4 if (someCondition) {

5 sync();

6 return result1;

7 } else {

8 return result2;

9 }

```

Figure 2.5: Jumping over a sync() statement when someCondition evaluates to false.

#### **On-first-load strategy**

This strategy increases parallelism by postponing the sync statement until the first load of a variable in which one of the spawnable calls stores. In Fig. 2.2 that would be exactly where the sync is now, on line 11, because **result1** is loaded first.

Unfortunately, this places multiple syncs in case of loops. In Fig. 2.4 this would mean that the sync statement is placed inside the loop between lines 12 and 13. It is preferable to put the sync in front of the for-loop, but it is not a problem since multiple syncs are allowed.

The strategy fails in the example in Fig. 2.5. When someCondition evaluates to false, there would be no sync and the result would be incorrect.

This can easily be solved by inserting sync statements in front of all loads of local variables in which spawn results are stored. However, there is a larger problem. The correctness is based on the assumption that loads always occur in the instruction range behind the spawnable call. In many cases this will be true, but there may be situations with a backward jump after a spawnable call. The analysis has to be control-flow aware to place sync statements in these situations. However, within basic blocks, where no control-flow occurs, the on-first-load strategy suffices.

#### Control-flow-aware strategy

The problems discussed above are solved with this strategy. It succeeds in placing the sync in front of both loads in Fig. 2.5 and, for example, just in front of a loop that accesses the result of a spawn (Fig. 2.4).

With help of control-flow information provided by the BCEL library [10], a

graph of *basic blocks* is constructed. A *basic block* is a sequence of instructions with only one entry and one exit point. So, within the basic block there is no branch instruction other than the last instruction and no instruction is targeted by any branch instruction except the first. The basic block analysis maintains a successor relation between the basic blocks and determines whether a basic block is an *ending basic block* in the graph. This is the case if the last instruction is a **return** or a **throw** instruction.

A *path* is a sequence of basic blocks, one a successor of the other. An *ending path* is a path where the last basic block is an ending basic block. For every spawnable call in the method the following analysis takes place: find all *ending paths* from the spawnable call on. This includes all possible loops.

Then, for every ending path, the implementation of this strategy tries to construct a *store-to-load path* for every local variable index in which the spawnable call stores. Note that there can be multiple local variable indices when spawnable calls return using exceptions. A *store-to-load path* is a path from the basic block of the spawnable call to a basic block with a load of one of the local variables in which the spawnable call stores.

In this stage, all spawnable calls of the spawnable method have been analyzed, and every spawnable call is associated with one or more store-to-load paths. The implementation retrieves all these paths and removes duplicates. For all these paths, it tries to find a basic block from the end that is not in a loop. The result is now one or more basic blocks in which a sync needs to be placed.

For each of these basic blocks, the on-first-load strategy finds the first load of a variable in which one of the spawnable calls stores, and this instruction is proposed as an instruction in front of which a sync statement should be inserted.

In the case that a spawnable method signature is of type void, results of a spawnable call are not read, or exceptions are not handled (there is no catch block), it is not possible to create a store-to-load path. In this case sync statements will be placed at the ends of all ending paths. This means that on every exit from the method, a sync will be placed.

The control-flow-aware strategy contains two additional optimizations:

**Unnecessary sync statements** It is possible that a spawning method contains multiple exclusive store-to-load paths, but where the sync statement is placed in such a way that it syncs the other paths as well. In this case it is not necessary to insert later sync statements. An example is Fig. 2.6. There is a path *without* the first read on line 7 and then *with* the second read on line 12,

```

1 for (int i = 0; i < MAX_SPAWNS; i++) {

\mathbf{2}

result[i] = spawnableMethod();

3 }

4

5 sync(); // placed by sync generator

6 for (int i = 0; i < MAX_SPAWNS; i++) {

7

readFirstTime(result[i]);

8 }

9

10 // sync left out by sync generator

11 for (int i = 0; i < MAX_SPAWNS; i++) {

12

readSecondTime(result[i]);

13 }

```

Figure 2.6: Multiple exclusive store-to-load paths.

which is exclusive from the path *with* the first read and *without* the second read. Without this optimization, the sync generator would also place a sync in front of the third for-loop on line 10. However, because there is already a sync in front of the second for-loop, the second sync is left out.

Array stores and object putfield If a spawnable call stores into an object, the load in a store-to-load path is based on the load of the object reference. In many cases, the load is used to read from the object, which needs a sync statement. However, there are situations in which the load of an object reference is used to store into the object, for example a store into an array or to store something in a field of an object. This does not need a sync statement.

Figure 2.7 shows a store into an array on line 8. The object reference for **result** needs to be loaded. Because of this, without optimization, the sync generator would insert a sync in front of the load. However, this optimization recognizes that the load of the object references is used for a store into an array or object field and places it beyond the load of the object reference on line 10.

#### Alias-aware strategy

The previous strategy places sync statements optimally in many cases, but the analysis is incorrect when *aliases* to object references are loaded instead of the *original* object references. Figure 2.8 illustrates this. On line 8 and 9, two result objects are created, and on line 10 and 11 new references are pointing to the same objects. The results are stored using references r1 and r2 (lines 13

```

1 for (int i = 1; i < MAX_SPAWNS; i++) {

2   result[i] = spawnableMethod();

3 }

4

5 // the reference to object result is loaded,

6 // but sync is not placed here, because it

7 // is a store into an array

8 result[0] = someValue;

9

10 sync(); // by sync generator

11 for (int i = 0; i < MAX_SPAWNS; i++) {

12   read(result[i]);

13 }</pre>

```

Figure 2.7: Ignoring array stores.

and 14), but the results are loaded using the aliases a1 and a2 (line 16). The sync() on line 17 is incorrectly placed.

Alias analysis is typically imprecise [11], but aliasing within a spawning method is not so common in the Satin programming model. Therefore, we take a pragmatic approach and try to detect situations where aliasing can occur.

Aliases introduced *after* the spawnable call has executed can only be introduced by loading the original object reference. The implementation detects this as a load and will insert a sync in front of the load. Therefore, aliases that are introduced after the spawnable call has executed do not need special treatment for providing correctness.

Aliases that are introduced *before* the spawnable call has executed do pose a problem. Spawnable calls that store into parameters of the spawning method form a special case. Aliases to these parameters could have been created before the spawning method was called, and since the implementation has no knowledge of these aliases, it reverts back to the fallback strategy and issues a warning. For aliases that are created within the method, as shown in Fig. 2.8 on lines 10 and 11, are handled by the alias-detection algorithm.

The alias-detection algorithm proceeds as follows: if a spawnable call stores into an object, it is necessary to check for aliases. If the object is a parameter of the spawning method, the analysis stops, gives a warning, and reverts back to the fallback strategy. Otherwise, the analysis uses the control-flow graph to find all predecessors of the basic block that contains the spawnable call. For every predecessor, the analysis determines whether the object is loaded or stored. If the object is loaded, it may be introducing an alias, unless the load instruction

#### 2.4 Implementation

```

1 class Result {

2

int v;

3 }

4

5 int spawningMethod() {

6

if (stopCondition) return 0;

7

8

Result r1 = new Result();

9

Result r2 = new Result();

10

Result a1 = r1;

11

Result a2 = r2;

12

13

r1.v = spawnableMethod();

14

r2.v = spawnableMethod();

15

16

int sum = a1.v + a2.v;

17

sync(); // incorrect, should be on line 15.

18

return sum:

19 }

```

Figure 2.8: Incorrect sync placement due to aliasing within a spawning method.

is used in the following cases: an array load or store, retrieving the length of an array, or putting data into or retrieving data from a field of the object. If the object reference is stored into, it may be introducing aliases unless it is used in the following situations: a *non-escaping constructor*, a cast, creating a one- or multi-dimensional array, or setting the reference to null.

A non-escaping constructor is a constructor of an object in which the this reference does not escape. To verify this, the analysis checks every instruction of the constructor. If the this reference is used, it may only be used for putting something into a field or calling the constructor of the super-class. These super-class constructors are verified recursively as well. The constructor of Object is non-escaping.

As a result of this algorithm, many situations that are common in Satin programs and that do not introduce aliases are detected, such as array creation, object creation, and putting data into a field. As soon as the object references are used for different reasons, and the analysis cannot guarantee that aliases are not introduced, the sync generator reverts back to the fallback strategy and gives a warning that aliases may have been created and that the sync placement is likely to be sub-optimal (but still correct).

For example, in the Satin programming model, the results of a spawnable

call are often stored into an array, for instance similar to Fig. 2.7. As the array often needs to be created first, this means that the object reference is stored into before the spawnable calls are executed. The alias-detection algorithm recognizes that this does not introduce aliases.

It is also common that results are stored in a result object, similar to r1 and r2 on lines 8 and 9 of Fig. 2.8. The class is defined on line 1. The aliasdetection algorithm recognizes the creation of a new object and performs the escape analysis on the default constructor. Also in this case, it concludes that the statements on line 8 and 9 do not introduce aliases.

However, on line 10 and 11, the object references r1 and r2 are loaded but do not comply to the cases outlined above. The alias-detection algorithm concludes that aliases may have been introduced here, reverts back to the fallback strategy, and warns for non-optimal sync placement.

To summarize: the alias-aware strategy cannot optimally place sync statements when a spawnable call stores into object references, except for the cases described above. However, it can detect possible aliasing and warn for nonoptimal sync placement. This gives the programmer the opportunity to either restructure the code to reduce possible aliasing, or insert sync statements manually.

# 2.5 Evaluation

The sync generator is evaluated using 35 pre-existing real-world Satin applications, amongst others a SAT solver [12], N-body simulation [7], Grammar-based text analysis [12], Grammar induction [7], Gene sequence alignment [7], FFT, and Game-tree search [13].

To evaluate the performance of the sync generator, the applications are stripped from sync statements. The applications are recompiled with the Satin compiler that runs the sync generator pass. The resulting bytecode is carefully examined and compared to the original bytecode. The placement of sync statements is compared in relation to the control-flow and variables on which the correctness and amount of parallelism depends.

The placement is said to be optimal, if it is as late as possible in the controlflow and allows all spawnable calls to run in parallel. The placement by the sync generator may be later in the control-flow than the placement of the programmer (but still correct). The sync generator may also place sync statements in such a way that sync is called multiple times. This has a negligible performance effect.

Table 2.1 shows the results. The first column shows the name of the ap-

## 2.5 Evaluation

Table 2.1: Automatic sync statement generation in real-world Satin applications.

| application                                                  | optimal | alias warning | notes                                                 |

|--------------------------------------------------------------|---------|---------------|-------------------------------------------------------|

| Adaptive integration                                         | yes     | -             | programmer placed un<br>necessary syncs               |

| Awari: game tree search<br>with the mtdf algo-<br>rithm [13] |         |               |                                                       |

| Reference version with<br>transposition tables               | yes     | -             |                                                       |

| Pre-allocated transposi-<br>tion tables                      | yes     | -             |                                                       |

| Transposition tables as<br>structure of arrays               | yes     | -             |                                                       |

| Replicated transposition<br>tables with Java RMI             | yes     | -             |                                                       |

| Replicated transposition<br>tables with sockets              | yes     | -             |                                                       |

| No speculative paral-<br>lelism                              | yes     | -             |                                                       |

| Shared objects version                                       | yes     | -             |                                                       |

| Binomial coefficients                                        | yes     | -             | programmer placed un<br>necessary syncs               |

| Checkers                                                     |         |               |                                                       |

| Reference version                                            | yes     | -             |                                                       |

| Negamax search with<br>alpha-beta pruning                    | no      | no            | based on false dependency                             |

| Fast Fourier Transform<br>(FFT)                              | yes     | -             | originally incorrect, con<br>rected by sync generator |

| Fifteen puzzle, iterative<br>deepening A* algo-<br>rithm     | yes     | -             | programmer placed un<br>necessary syncs               |

| Gene sequence align-<br>ment [7]                             | yes     | -             |                                                       |

| Grammar induction [7]                                        | yes     | -             |                                                       |

| Grammar-based text<br>analysis [12]                          | yes     | -             |                                                       |

| Knapsack                                                     | yes     | -             |                                                       |

|                                                              |         |               | Continued on next pag                                 |

| application                                                         | optimal | alias warning  | notes                                                           |

|---------------------------------------------------------------------|---------|----------------|-----------------------------------------------------------------|

| Matrix multiplication                                               |         |                |                                                                 |

| Standard version                                                    | no      | $\mathbf{yes}$ | writing into parameter                                          |

| shared objects version                                              | no      | $\mathbf{yes}$ | writing into parameter                                          |

| N-body simulation<br>(Barnes-Hut) [7]                               | yes     | -              |                                                                 |

| N-Queens problem                                                    |         |                |                                                                 |

| Reference version                                                   | yes     | -              |                                                                 |

| Using exceptions                                                    | yes     | -              |                                                                 |

| Using speculative paral-<br>lelism and aborts                       | yes     | -              |                                                                 |

| Using speculative par-<br>allelism, aborts and<br>thresholding      | yes     | -              |                                                                 |

| Non-speculative version,<br>counting total num-<br>ber of solutions | yes     | -              |                                                                 |

| 2nd prize winner in the<br>Grids@work 2005<br>contest [14]          | no      | yes            | writing into object refer-<br>ence, writing into param-<br>eter |

| Othello: game tree search<br>with the mtdf algo-<br>rithm [13]      | yes     | -              |                                                                 |

| Prime factorization                                                 | yes     | -              |                                                                 |

| Raytracer                                                           | yes     | -              |                                                                 |

| SAT solver [12]                                                     | yes     | -              |                                                                 |

| Text indexing                                                       | yes     | -              |                                                                 |

| Traveling Salesman Prob-<br>lem                                     |         |                |                                                                 |

| Reference version                                                   | yes     | -              |                                                                 |

| Shared objects version                                              | yes     | -              |                                                                 |

| Young-brothers-wait<br>version                                      | yes     | -              |                                                                 |

| VLSI cell router (Locus-<br>Route) [15, 16]                         | yes     | -              |                                                                 |

#### 2.5 Evaluation

plication. Column two shows whether the generated syncs are inserted at an optimal place. In the case that sync statements are not placed optimally, the third column indicates whether the programmer receives a warning due to aliasing. Column four shows some additional notes.

The table does not show whether the applications are correct, because this is true for all the applications. Correct means that the applications with automatically inserted sync statements give the same result as the original applications.

The overall result is that the sync generator is able to compute an optimal sync placement for 31 out of the 35 applications. In the application FFT, the sync generator inserted correct sync statements that were missing in the original incorrect application. We also tested the sync generator on 12 additional test applications, such as a Fibonacci application and a hello world application. Because the placement is optimal in all cases and these applications are not real-world applications, we do not discuss these applications.

There are some applications that print the timing measurements incorrectly with automatically inserted syncs. Programmers often measure execution time behind the sync statement, but the sync generator postpones the sync beyond this measurement. We do not regard this as a problem as programmers will place the timing statements differently when relying on the sync generator.

## 2.5.1 Evaluation per application

To get more insight in the results, we discuss the applications separately. The applications that have optimal sync placement and no further problems are omitted.

Adaptive integration, Binomial coefficients, Fifteen puzzle In these applications the programmer placed syncs where the sync generator leaves them out. The sync generator is correct and these syncs can be safely left out. This shows that unnecessary sync insertion is no problem.

**Checkers (negamax version)** This application is the only application that does not have optimal placement and has no warning. Figure 2.9 shows the cause. The method srch() has a variable beta\_cutoff that has value 0 initially. Depending on this value, the control-flow breaks out of the for-loop (line 19). The programmer knows that this variable is not important for the result, only for performance. The sync generator must regard the variable beta\_cutoff as a variable in which some value is stored inside the catch block (line 13). This

```

1 void srch() throws Result {

2

int beta_cutoff = 0;

3

4

for (x = 0; x < count; x++) {</pre>

\mathbf{5}

// sequential work

6

try {

7

spawn_srch();

}

8

9

catch (Result res) {

10

killer[p.ply] = move_list[res.choice_ix];

11

// other stuff

12

if (-res.score >= p.beta) {

13